Maskable and non-maskable interrupts are two kinds of interrupts in the CPU. The interrupt that can be ignored by the CPU is the maskable interrupt. The interrupt that cannot be ignored and is reserved for some important events is a non-maskable interrupt.

Maskable and non-maskable interrupts are two kinds of interrupts in the CPU. The interrupt that can be ignored by the CPU is the maskable interrupt. The interrupt that cannot be ignored and is reserved for some important events is a non-maskable interrupt.

What is Interrupt?

An interrupt is a way to break the normal sequencing of the processor in order to perform some specific task. Let us understand interrupts in the operating system using a day to day example.

- Consider that you are reading a book (currently running a program). While you are reading, the doorbell rings (interrupt occurred).

- You put the bookmarker on the current page and down the book. After that, you will heads towards the door (start executing a new program as it is of higher priority than reading a book).

- Now you are attending to the person at the door (performing the Interrupt Service Routine), the phone bell rings in mid of your conversation (another interrupt occurred).

- Now seeking the excuse of the person at the door you head to attend the phone call. Next, you receive the phone call (start executing the new program as it is of higher priority than attending to a person at the door and reading a book). This is the scenario of nested interrupts.

Similarly, in our computer system, there can occur multiple interrupts. However, a specific priority is set for each interrupt. If multiple interrupts occur at a time, the computer knows which interrupt it must process first.

Well, we can program the processors to accept or reject the occurred interrupt using:

- Maskable Interrupt

- Non-maskable interrupts.

In this content, we are going to discuss the differences between maskable and non-maskable interrupts. We will also be discussing these terms in detail along with the example.

Content: Maskable Vs Non-Maskable Interrupt

- Comparison Chart

- Types of Interrupts

- What is Maskable Interrupt?

- What is Non-Maskable Interrupt?

- Key Differences

- Conclusion

Comparison Chart

| Basis of Comparison | Masked Interrupts | Non-Maskable Interrupts |

|---|---|---|

| Basic Concept | The processor can accept or reject the maskable interrupts. | The processor has to accept the non-maskable interrupts. |

| Processing | The maskable interrupt is processed immediately if the interrupt occurred has higher priority than currently executing instruction. Else the interrupt is processed after completing the current execution. | The non-maskable interrupt has to be processed as soon as it occurs by suspending the current execution. |

| Priority | Interrupts with low priority are the maskable interrupts. | Interrupts with high priority are non-maskable interrupts. |

| Vector Address | The vector address of maskable interrupt can be altered by programming the Interrupt Controller. | The vector address of non-maskable interrupt are fixed and are predefined by the manufacturer of the processor. |

| Use | Maskable interrupts are used by the device controllers. | Used by watch dog timer and during power failure. |

| Example | In 8085 microprocessor all the hardware interrupt excluding TRAP are maskable interrupt. | In 8085 the interrupts raised TRAP pin and all software interrupts are non-maskable interrupt. |

Types of Interrupts

The system can generate interrupts in the following ways:

- By an external signal, generated by the hardware.

- Using an internal signal, generated by the software.

- By an internal signal, generated due to some exceptional condition that occurs while executing a specific instruction in the program.

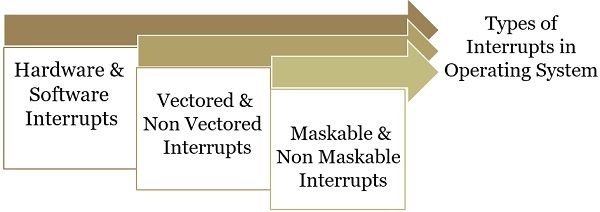

Further, we can classify interrupts into three categories:

- Hardware and Software Interrupt

- Vectored and Non-Vectored Interrupt

- Maskable and Non Maskable Interrupt

Whenever hardware or software wants to seek the attention of the processor, they signal an interrupt to the processor. The hardware interrupts the processor by sending the signal through a peripheral device. The software interrupts the processor by executing a specific instruction.

The program control automatically branches to a specific address when a vectored interrupt occurs. This specific memory address is a vector address and it stores ISR (Interrupt Service Routine). For vectored interrupt, the manufacturer of the processor predefines this vector address.

The vector address of non-vectored interrupt is not predefined. In fact, it is the interrupting device that provides the address of the ISR that the processor must execute in response to the occurred interrupt.

Maskable interrupts are the ones that the processor can accept or reject. However, non-maskable interrupts are the ones that the processor has to accept as soon as they occur.

What is Maskable Interrupt?

The CPU has two interrupt request lines. One is the maskable interrupt and the other is the non-maskable interrupt. When the maskable interrupt occurs the processor can accept or reject it on the basis of its priority.

- If the priority of the interrupt is lower than the instruction currently in execution then the processor rejects the occurred interrupt.

- If the priority of the occurred interrupt is higher than the instruction currently in execution then the processor suspends the current execution and accepts the occurred interrupt.

Usually, the low priority interrupts are maskable interrupts. For example, the device controller uses the maskable interrupt to request services from the processor.

By programming the Interrupt controller, we can change the maskable interrupt’s vector (address of specialized ISR).

What is Non-Maskable Interrupt?

When the non-maskable interrupt occurs, the processor has to accept it. Because these interrupts are raised for the events that are important and have to be attended by the processor. The non-maskable interrupts are high priority interrupts. Such as unrecoverable memory errors, power failure, etc.

Whenever the non-maskable interrupt occurs the processor suspends its current execution and accepts the occurred interrupt.

The vector i.e. the memory address to the Interrupt Service Routine is fixed for the non-maskable interrupt.

Key Differences Between Maskable and Non-Maskable Interrupts

- Maskable interrupts are the ones that the processor can accept or reject on the basis of their priority. On the contrary, the non-maskable interrupts are the ones that the processor has to accept.

- Consider that the processor is currently executing some process and the maskable interrupt occurs. Now if the occurred interrupt is of higher priority than the currently executing process then the processor accepts the interrupt and if it is of a lower priority then the processor ignores the interrupt.

Now consider that processor is currently executing some processes and the non-maskable interrupt occurs. Then the processor suspends its current execution and immediately accepts the occurred interrupt. - The maskable interrupt helps in handling low priority tasks. Whereas the non-maskable interrupt helps in handling high priority tasks.

- By programming the Interrupt Controller, we can modify the maskable interrupt’s vector address (holding the specific interrupt-handling routine). On the other hand, the vector address of the non-maskable interrupt is fixed and predefined by the processor’s manufacturer.

- Generally, the peripheral devices or the device controllers make use of the maskable interrupts. However, the non-maskable interrupts are used for handling events such as power failure, unrecoverable memory errors etc.

- In the 8085 microprocessor, all the hardware interrupts excluding the TRAP are maskable interrupts. Whereas, the interrupt raised by the TRAP pin and all the software-initiated interrupts are the non-maskable interrupts.

Conclusion

The interrupts are critical events that require the attention of the processor. However, the maskable interrupts are the ones that the processor can either accept or reject. But the non-maskable interrupts are the ones that the processor has to accept.

Leave a Reply